Input Impedance Chopper Stabilized Amplifier with Dual Feedback Loops

Input Impedance Technique 3

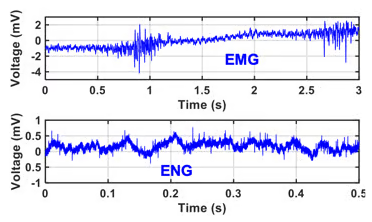

Architecture

CCIA(Capacitively-coupled Chopper Instrumental Amplifier) core with RRL(Ripple Reduction Loop) & SS-DSL(Single-slope-assisted DC-servo Loop)

PGA and 10b SAR ADC

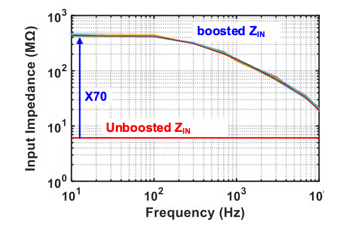

DPFL(Dual Positive Feedback Loops) for impedance boosting

Signal generator and automatic calibration logic for external parasitics adaptation

Characteristics

Verified IP

CCIA(Capacitively-coupled Chopper Instrumental Amplifier) core with RRL & SS-DSL

PGA and 10b SAR ADC

DPFL(Dual Positive Feedback Loops) for impedance boosting

Signal generator and automatic calibration logic for external parasitics adaptation

Power Supply : 1.5V/1.0V

Power Consumption : 3.83uW

Bandwidth : 1Hz ~ 1kHz

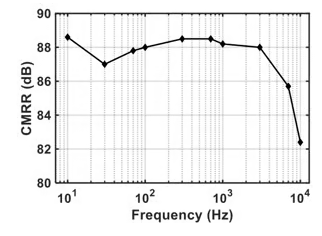

CMRR : 92dB

PSRR : 100dB

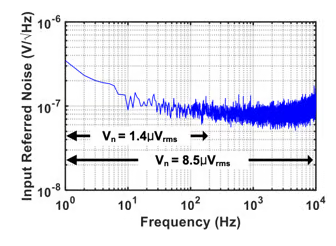

Input Referred Noise : 0.36 µV/√Hz at 300Hz BW

Dynamic Range : 87.3dB

Peak Input : 560mVpp

Zin at DC : over 15GΩ

Zin at Bandwith(50Hz) : 2GΩ

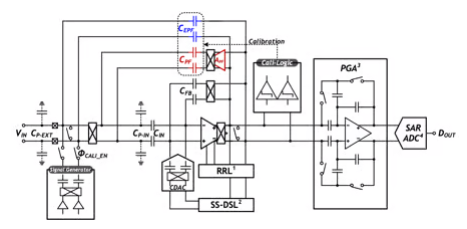

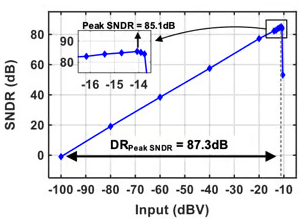

Performance - SNDR, IRN, CMRR

SNDR(Signal to Noise/Distortion Ratio) : 85.1dB at 1kHz BW

IRN(Input Referred Noise) : 1.4 µV/√Hz at 200Hz(8.5 µV/√Hz at 10kHz)

CMRR(Common Mode Rejection Ratio) : over 82dB

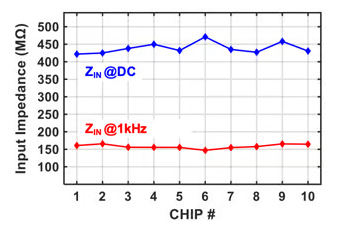

Performance - ZIN

Zin(Input Impedance) : over 421MΩ at DC(147MΩ at 1kHz)

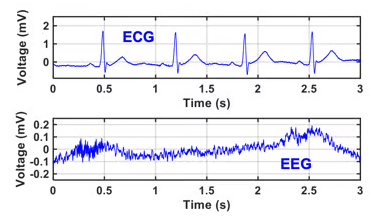

Performance - True ExG Acquisition